# CS444/544 Operating Systems II

Lecture 11

#### Virtualization Summary and Quiz 2 Prep

5/8/2024

Acknowledgement: Slides drawn heavily from Yeongjin Jiang

### Odds and Ends

- Lab 2 will be graded by this weekend

- Quiz 2 on Monday (more info later)

# Today's Topic

- Virtualization -> Concurrency

- OS Three Easy Pieces

- Virtualization (memory, process, user/kernel, etc.)

- Concurrency (multi-threading, multi-process, scheduling, synchronization)

- Persistence (disk, file, snapshot, etc.)

- Do recap on Virtualization

- Quiz 2 Prep.

#### What is an OS?

Applications

Hardware

## Memory

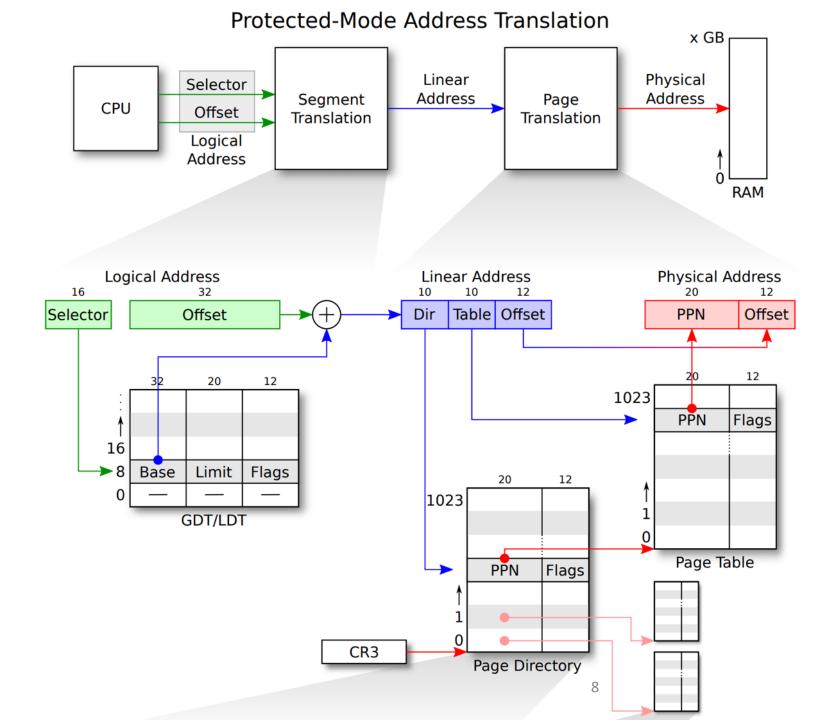

Backward compatibility: BIOS will put the code that assumes your CPU as i8086 (a 43-years old 16-bit CPU). So we need to start with 16-bit mode and then enable 32-bit protected mode, paging, etc...

UEFI does not go through this process; they directly starts with 32-bit or 64-bit mode, so OSes do not have to handle these things..

- 8086 Segmentation Real Mode

- Address = seg \* 16 + offset

- 80386 Segmentation Protected Mode

- GDT defines base and limit

- seg selects a GDT entry

- Address = GDT[seg].base + offset

| 31 16     |    |     |     |            |            |    |           |      | 0     |

|-----------|----|-----|-----|------------|------------|----|-----------|------|-------|

| Base 0:15 |    |     |     |            |            |    | Limit     | 0:15 |       |

| 63 !      | 56 | 55  | 52  | 51         | 48         | 47 | 40        | 39   | 32    |

| Base 24:3 | 1  | Fla | igs | Lir<br>16: | nit<br>:19 | Ac | cess Byte | Base | 16:23 |

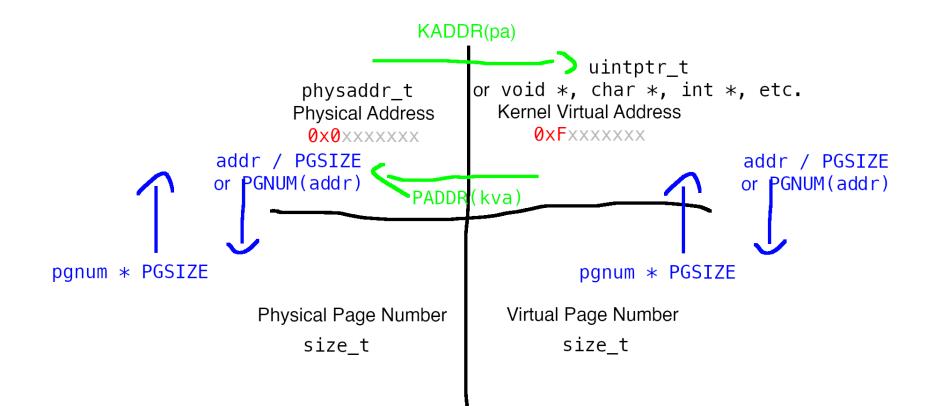

### **Virtual Memory**

- Paging

- When enabled, all memory address will be translated via

- CR3 -> PDE -> PTE -> Physical Page!

#### **Recap** – Page Table & Addr Translation

|           | 31         |                                      |                           | 12   |                                          | 0     | Virtual                  | Physical                                           |               |          |  |

|-----------|------------|--------------------------------------|---------------------------|------|------------------------------------------|-------|--------------------------|----------------------------------------------------|---------------|----------|--|

|           | 0x08048000 |                                      |                           |      |                                          |       |                          |                                                    | 0x8048000     | 0x10000  |  |

|           |            |                                      |                           |      |                                          |       |                          | 0x8049000                                          | 0x11000       |          |  |

|           |            | Page number (20-bits)<br>0x08048     |                           |      |                                          |       | t (12-bits)<br>x000      |                                                    | 0x804a000     | 0x50000  |  |

| CR3[0x20] |            | Directory Index<br>(10-bits)<br>0x20 |                           | (1   | Table index<br>(10-bits)<br><u>0x</u> 48 |       |                          |                                                    |               |          |  |

|           | 31 22 1    |                                      | L2 Phy. Pa                |      | Page number (20-bits) Of<br>0x10000      |       | ffset (12-bits)<br>0x000 |                                                    |               |          |  |

|           | Pa         | ge Directory Entry                   |                           |      | Page Table                               | Entry |                          |                                                    |               |          |  |

| 0         | Ad         | ldr PT                               |                           | 0    | Addr PT                                  |       | nde t*                   | pd = KADDR                                         | (lcr3())·     |          |  |

|           | Ad         | ddr PT                               | 101                       | 0x48 | 0x10000                                  |       | - —                      | -                                                  | TE_ADDR(pd[PD | X(va)])) |  |

| 0x20      | Ad         | ldr PT                               | PDE[0x48]<br>0x49 0x11000 |      | 0x11000                                  |       | physado                  | physaddr_t paddr = PTE_ADDR(pt[PTX(va)]) + PGOFF(v |               |          |  |

| 0x3ff     | Ad         | ldr PT                               |                           | 0x4a | 0x50000                                  | 7     |                          |                                                    |               |          |  |

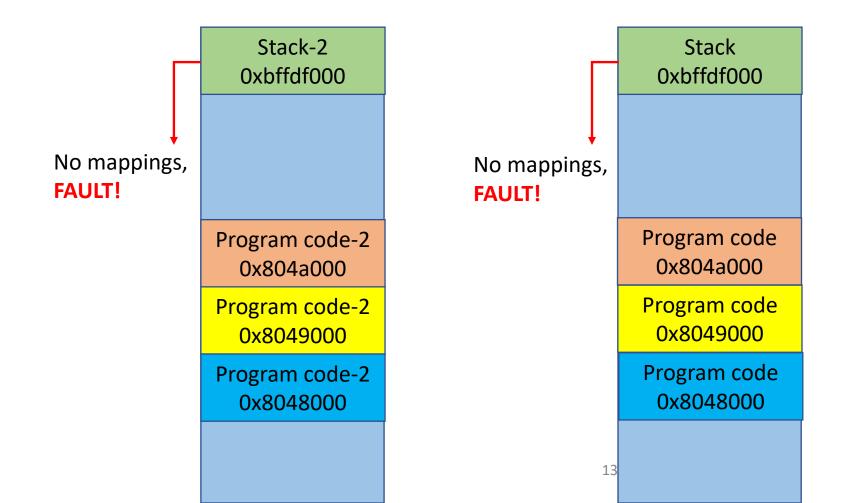

# Why Virtual Memory?

- Three goals

- Transparency: does not need to know system's internal state

- Program A is loaded at 0x8048000. Can Program B be loaded at 0x8048000?

- Efficiency: do not waste memory; manage memory fragmentation

- Can Program B (288KB) be loaded if 288 KB of memory is free, regardless of its allocation?

- Protection: isolate program's execution environment

- Can we prevent an overflow from Program A from overwriting Program B's data?

### Paging: Virtual Memory

Physical Memory

| • Havin                     | Stack-2<br>0x17000        |            |               |         |                           |

|-----------------------------|---------------------------|------------|---------------|---------|---------------------------|

| Stack-2                     | Stack                     | Virtual    | Physical      |         | Program code-2            |

| 0xbffdf000                  | 0xbffdf000                | 0x8048000  | 0x10000       |         | 0x16000                   |

|                             |                           | 0x8049000  | 49000 0x11000 |         | Program code-2<br>0x15000 |

|                             |                           | 0x804a000  | 0x14000       |         |                           |

|                             |                           | 0xbffdf000 | 0x12000       |         | Program code<br>0x14000   |

| Program code-2<br>0x804a000 | Program code<br>0x804a000 |            |               |         | Program code-2            |

|                             | Program code<br>0x8049000 | Virtual-2  | Physical-2    |         | 0x13000                   |

| Program code-2<br>0x8049000 |                           | Ŭ          | 0x8048000     | 0x13000 |                           |

| Program code-2              | Program code              | 0x8049000  | 0x15000       | D       |                           |

| 0x8048000                   | 0x8048000                 | 0x804a000  | 0x16000       |         | Program code<br>0x11000   |

|                             |                           | 0xbffdf000 | 0x17000       |         | Program code              |

|                             |                           |            | 10            |         | 0x10000                   |

Transparency: does not need to know system's internal state Program A is loaded at 0x8048000. Can Program B be loaded at 0x8048000?

#### • Having an indirect table that maps virt-addr to phys-addr

| Stack-2        | Stack        | Virtual    | Physical   |  |

|----------------|--------------|------------|------------|--|

| 0xbffdf000     | 0xbffdf000   | 0x8048000  | 0x10000    |  |

|                |              | 0x8049000  | 0x11000    |  |

|                |              | 0x804a000  | 0x14000    |  |

|                |              | 0xbffdf000 | 0x12000    |  |

| Program code-2 | Program code |            |            |  |

| 0x804a000      | 0x804a000    | Mature 1.0 |            |  |

| Program code-2 | Program code | Virtual-2  | Physical-2 |  |

| 0x8049000      | 0x8049000    | 0x8048000  | 0x13000    |  |

| Program code-2 | Program code | 0x8049000  | 0x15000    |  |

| 0x8048000      | 0x8048000    | 0x804a000  | 0x16000    |  |

|                |              | 0xbffdf000 | 0x17000    |  |

|                |              |            | 11<br>     |  |

Stack-2 0x17000 Program code-2 0x16000 Program code-2 0x15000 Program code 0x14000 Program code-2 0x13000 Stack 0x12000 Program code 0x11000 Program code 0x10000

Physical Memory

#### Efficiency: do not waste memory Can Program B (288KB) be loaded if only 288 KB of memory is free, regardless of its allocation?

#### • Having an indirect table that maps virt-addr to phys-addr

| Stack-2        | Stack                     | Virtual    | Physical   |

|----------------|---------------------------|------------|------------|

| 0xbffdf000     | 0xbffdf000                | 0x8048000  | 0x10000    |

|                |                           | 0x8049000  | 0x11000    |

|                |                           | 0x804a000  | 0x14000    |

|                |                           | 0xbffdf000 | 0x12000    |

| Program code-2 | Program code              |            |            |

| 0x804a000      | 0x804a000<br>Program code | Virtual 2  | Dhysical 2 |

| Program code-2 |                           | Virtual-2  | Physical-2 |

| 0x8049000      | 0x8049000                 | 0x8048000  | 0x13000    |

| Program code-2 | Program code              | 0x8049000  | 0x15000    |

| 0x8048000      | 0x8048000                 | 0x804a000  | 0x16000    |

|                |                           | 0xbffdf000 | 0x17000    |

|                |                           |            | 12<br>     |

Stack-2 0x17000 Program code-2 0x16000 Program code-2 0x15000 Program code 0x14000 Program code-2 0x13000 Stack 0x12000 Program code 0x11000 Program code 0x10000

Physical Memory

Protection: isolate program's execution environment Can we prevent an overflow from Program A from overwriting Program B's data?

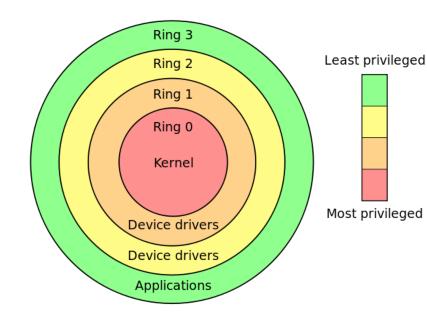

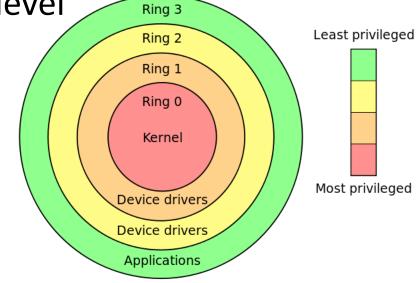

# Kernel (Ring 0)

- Runs with the highest privilege level (Ring 0)

- Configures system (devices, memory, etc.)

- Manages hardware resources

- Disk, memory, network, video, keyboard, etc.

- Manages other jobs

- Processes and threads

- Serves as trusted computing base (TCB)

- Set privilege, restrict other jobs from doing something bad, etc.

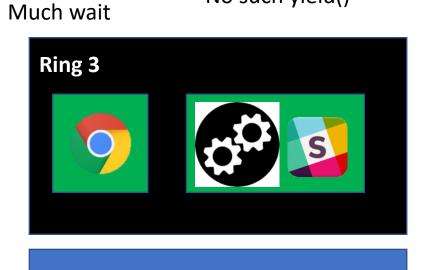

# User Level (Ring 3)

- Runs with a restricted privilege (Ring 3)

- The privilege level for running an application...

- Most of our regular applications runs in this ring level

- Cannot access kernel memory

- Can only access pages set with PTE\_U

- Cannot talk directly to hardware devices

- Kernel must mediate the access

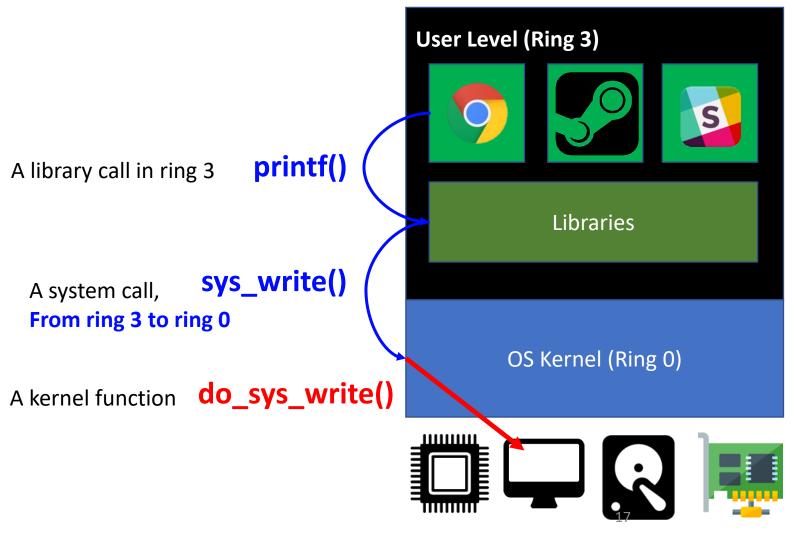

# A High-level Overview of User/Kernel Execution

# A High-level Overview of User/Kernel Execution

# A High-level Overview of User/Kernel Execution

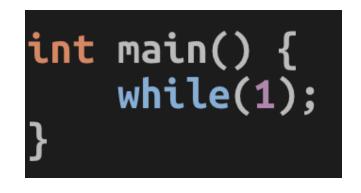

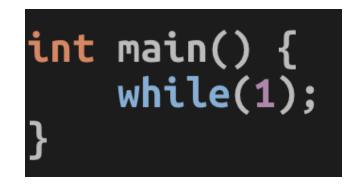

# User Execution Strawman 2'

Too long No such yield()

• What if a process runs

OS Kernel (Ring 0)

#### User Execution Strawman 2'

Too long

• What if a process runs

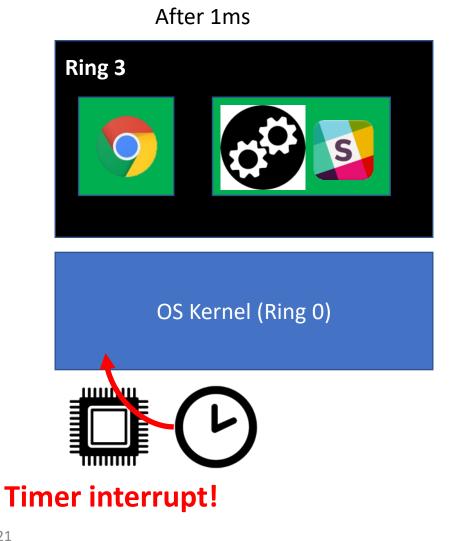

### **Recap: Timer Interrupt and Multitasking**

- Preemptive Multitasking (Lab 4)

- CPU generates an interrupt to force execution at kernel after some time quantum

- E.g., 1000Hz, on each 1ms..

### **Recap: Timer Interrupt and Multitasking**

- Preemptive Multitasking (Lab 4)

- CPU generates an interrupt to force execution at kernel after some time quantum

- E.g., 1000Hz, on each 1ms..

- Guaranteed execution in kernel

- Let kernel mediate resource contention

### **Recap: Timer Interrupt and Multitasking**

- Preemptive Multitasking (Lab 4)

- CPU generates an interrupt to force execution at kernel after some time quantum

- E.g., 1000Hz, on each 1ms..

- Guaranteed execution in kernel

- Let kernel mediate resource contention

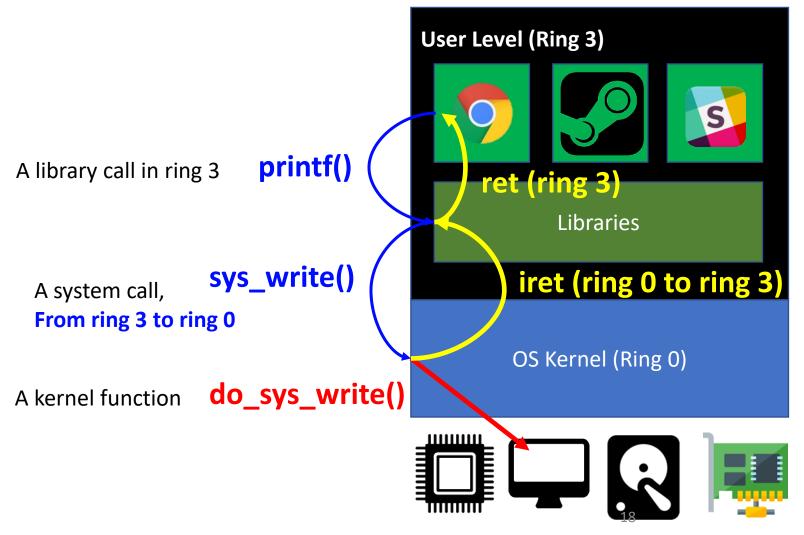

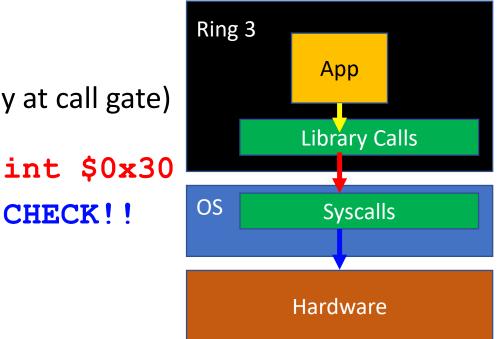

# **User/Kernel Switch**

- System call

- User calls Kernel APIs

- Kernel mediates API access (checks legitimacy at call gate)

- How switch?

- At the call gate, store trap frame

- Stores all registers, and other states

- On returning to user (iret)

- Restore all information from trap frame

# User/Kernel Switch

- Interrupts

- Could come from hardware (when it is not a software interrupt)

- Think about the timer interrupt

- Let OS do context switch!

- Steps

- Stops current process (stores trapframe)

- Runs kernel for handling the interrupt (refer to IDT)

- Resumes previous (or new) process (iret)

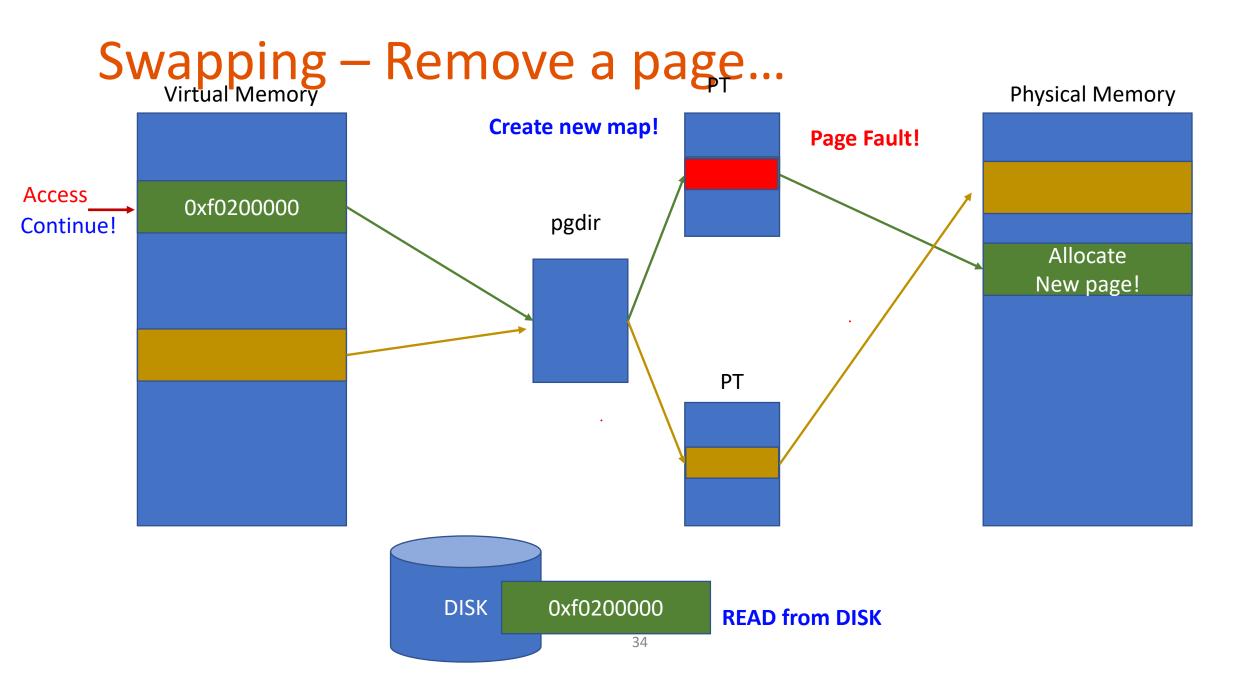

#### Faults

- An error that OS can recover

- Example

- Page fault

- Copy-on-write fork

- Memory Swapping

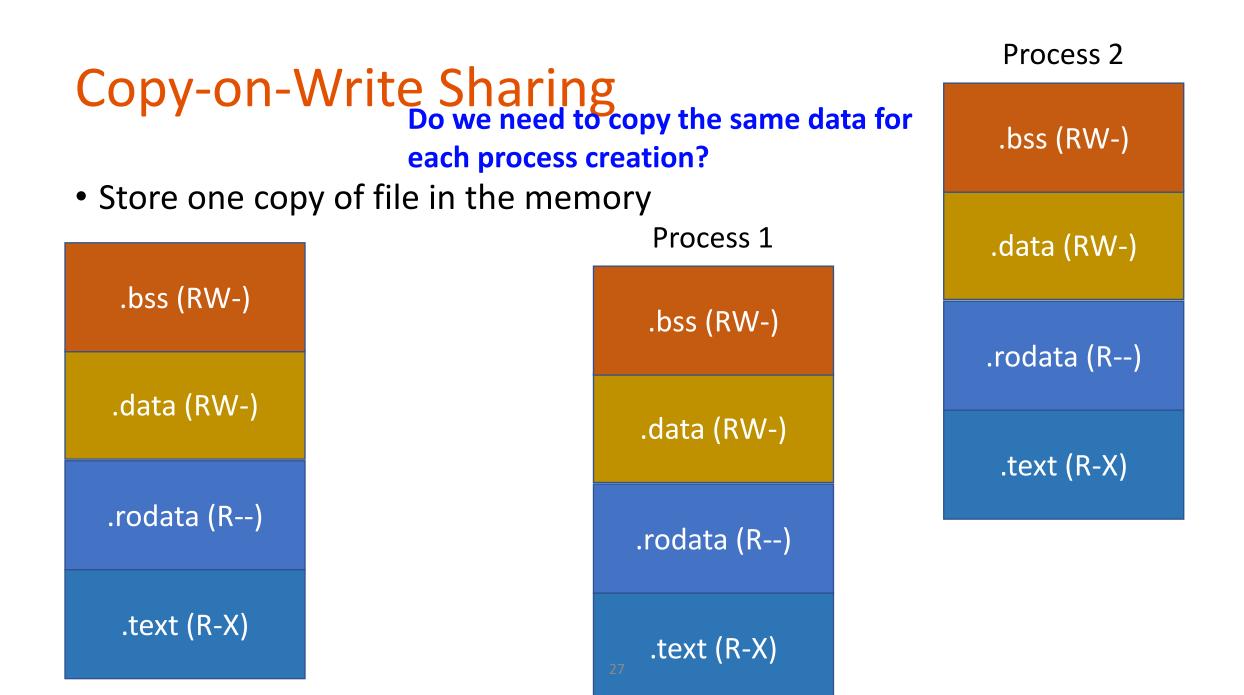

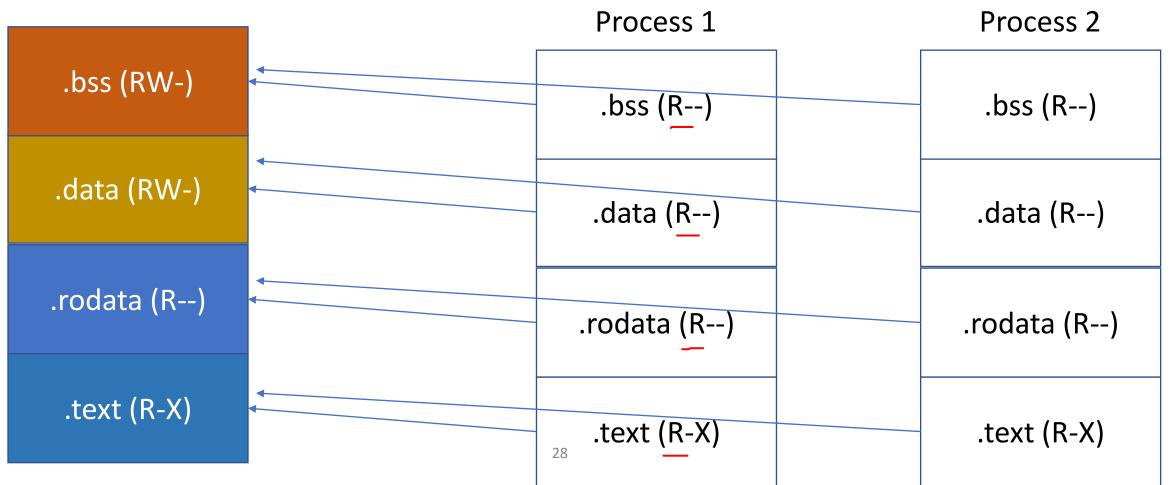

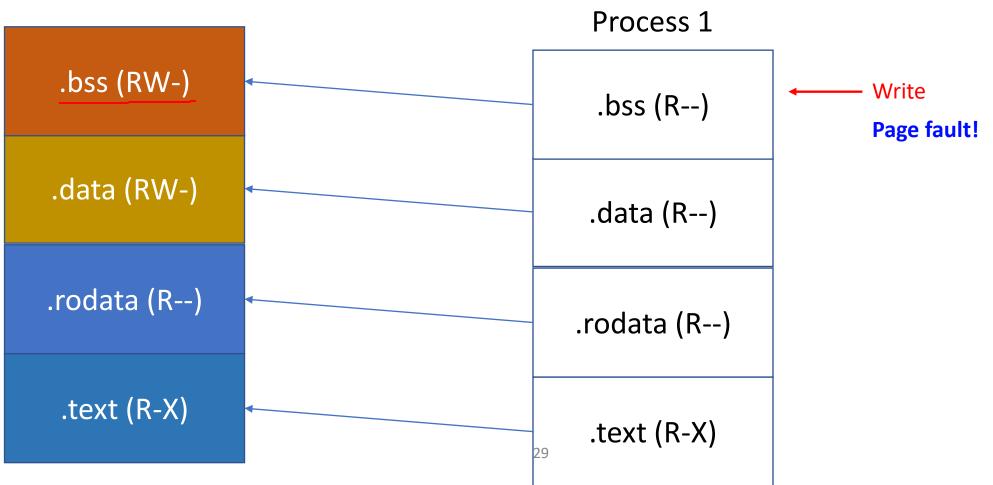

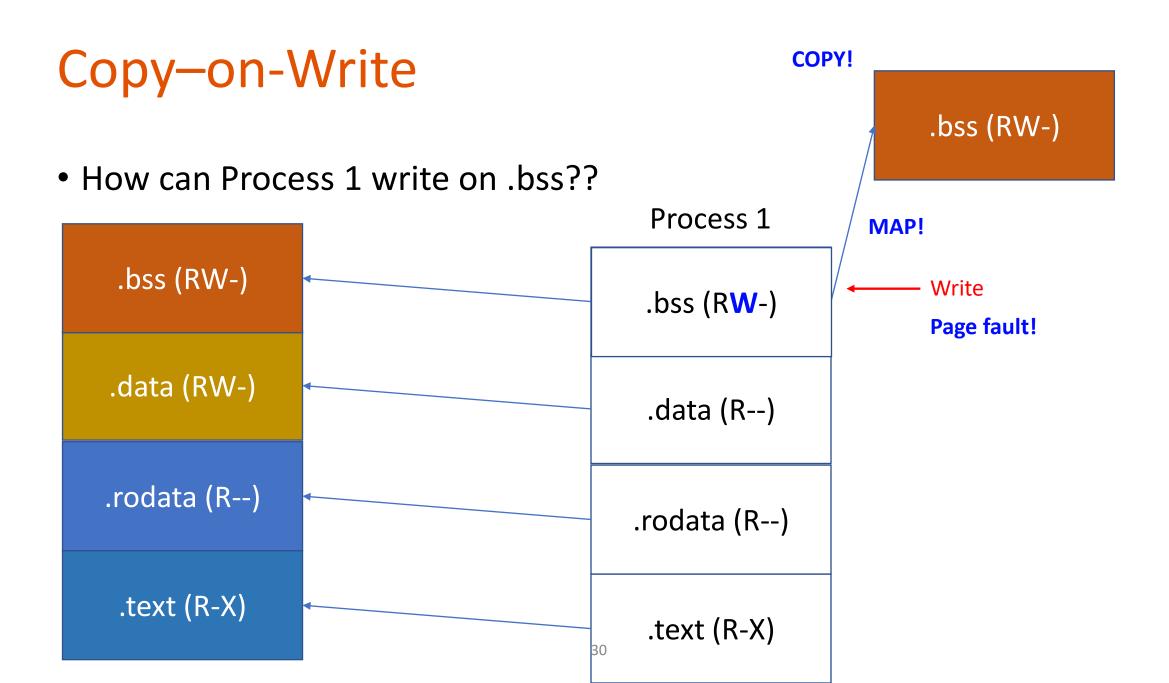

#### Sharing by Read-only

• Set page table to map the same physical address to share contents

#### Generate a Page Fault on Writing Attempt

• How can Process 1 write on .bss??

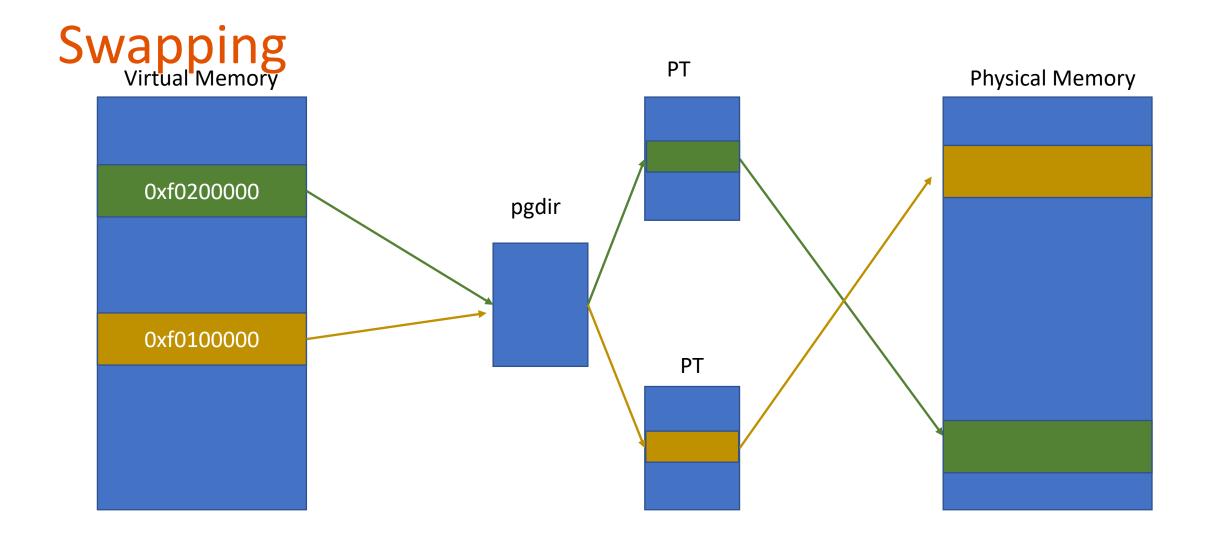

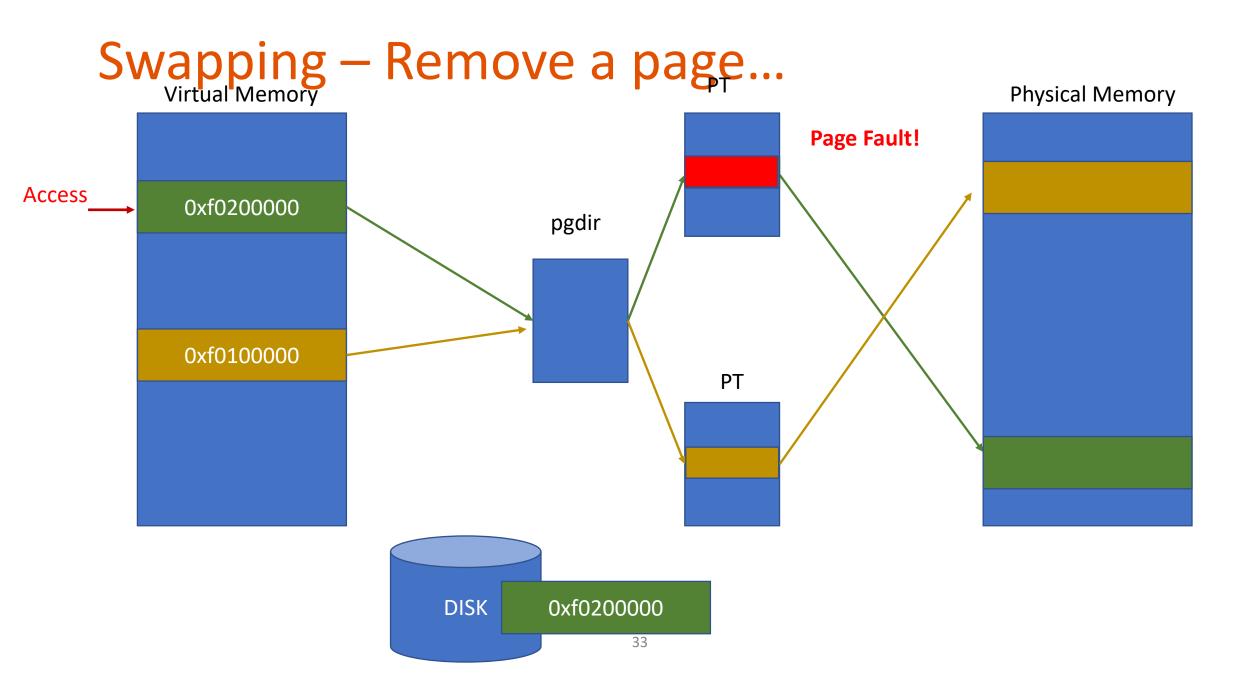

# A Challenge of Having Small Physical Memory

- Suppose you have 8GB of main memory

- Can you run a program that its program size is 16GB?

- Yes, you can load them part by part

- This is because we do not use all of data at the same time

- Can your OS do this execution seamlessly to your application?

#### Quiz 2

- Monday (5/13 from 8:00am to 11:59pm, 90 mins, 2 attempts)

- Open materials (slides, videos, code, and textbook)

- You will have 2 attempts for the quiz

# Quiz 2 Coverage

- JOS Lab 2 (Virtual Memory Management)

- JOS Lab 3 (User/Kernel, System Call and Interrupt Handling)

- Lecture 8: User/Kernel Context Switch

- Lecture 9: Handling Interrupt & Exceptions

- Lecture 10: System Calls, Call Gate, and Page Fault

- Lecture 11: Virtualization Review

- Memory Protection

- How does an OS/CPU apply access control to the virtual memory system?

- Protected mode (DPL), Page directory / page table (permission flags, PTE\_W & PTE\_U)

- How does an OS protect itself against the attacks from application code?

- Removing PTE\_U from PDE or PTE

- How does an OS protect the memory area which is supposed to be read-only from write attempts?

- Removing PTE\_W from PDE or PTE

- How does an OS isolate the memory space of a process from others?

- Having a new page directory / page tables

- Memory Overhead Calculation

- We have the following mapping for a program. How much of physical memory is required to support virtual to physical address translation for this program (get the minimal total size of page directory and page tables that enables this allocation)?

| Area               | Start virtual addr | End virtual addr | Size     |

|--------------------|--------------------|------------------|----------|

| .text (code)       | 0x800000           | 0x804000         | 0x4000   |

| .data (read/write) | 0x900000           | 0x902000         | 0x2000   |

| .bss               | 0xc00000           | 0xd00000         | 0x100000 |

Memory Overhead Calculation

In

0

1

2

3

•••

**0**x

|      |                             |                |       | l            |  |                              |               |       |                 |  |

|------|-----------------------------|----------------|-------|--------------|--|------------------------------|---------------|-------|-----------------|--|

|      |                             | Area           |       | Start virtua |  | dr                           | End virtual a | ddr 🖌 | Size            |  |

|      | .text (code)                |                |       | 0x800000     |  |                              | 0x804000      |       | 0x4000          |  |

|      | .data (read/writ            |                | te)   | 0x900000     |  |                              | 0x902000      |       | 0x2000          |  |

|      | .bss                        |                |       | 0xc00000     |  |                              | 0xd00000      |       | <u>0x100000</u> |  |

|      |                             |                |       |              |  | 0                            | x1000m        |       |                 |  |

| ndex | ndex Address range F        |                |       | PTE          |  | 1 page directory: 4KB        |               |       |                 |  |

| 1    | <u>/</u> 0x0~0x400000)      |                |       | invalid      |  |                              |               |       |                 |  |

|      | <u>/0</u> x400000 ~ 0x80000 |                | inval | invalid      |  | 2 page tables: 2 * 4KB = 8KB |               |       |                 |  |

|      | 0x800000 ~ 0xc00000 V       |                | valid | id           |  |                              |               |       |                 |  |

|      | 0xc00000 ~ 0x1000000 v      |                | valid | valid        |  | <u> </u>                     |               |       |                 |  |

|      | Ir                          |                | Inval | Invalid      |  |                              |               |       |                 |  |

| x3ff | 0xffc0000                   | 0 ~ Oxffffffff | Inval | valid        |  | 3                            | 9             |       |                 |  |

|      |                             |                |       |              |  |                              |               |       |                 |  |

9 อา - - ..

$\subset \mathfrak{log}$

d of

- User / Kernel Switch

- How does an OS get back the execution from the user while the user runs while(1);?

- Timer interrupt will preempt the execution from user to kernel

- How does the user program access the hardware? What's the job of the OS in this process?

- OS offers system calls (APIs available in OS)

- User program invokes system call via generating a software interrupt

- OS checks access to resources

- File, network, memory, etc.

- For an interrupt that has an error code,

- Which part of TrapFrame is prepared by the CPU?

41

- tf\_ss, tf\_esp, tf\_eflags, tf\_cs, tf\_eip and tf\_err

- Which part of TrapFrame is prepared by JOS?

- All others: tf\_trapno, tf\_ds, tf\_es, tf\_regs

| +                | -+ KSTACKTOP |

|------------------|--------------|

| 0x00000   old SS | " - 4        |

| old ESP          | " - 8        |

| old EFLAGS       | - 12         |

| 0x00000   old CS | - 16         |

| old EIP          | " - 20       |

| error code       | " - 24 < ESP |

| +                | -+           |

struct Trapframe { struct PushRegs tf\_regs; uint16\_t tf\_es; uint16\_t tf\_padding1; uint16\_t tf\_ds; uint16\_t tf\_padding2; uint32\_t tf\_trapno; /\* below here defined by uint32\_t tf\_err; uintptr\_t tf\_eip; uint16\_t tf\_cs; uint16\_t tf\_padding3; uint32\_t tf\_eflags; /\* below here only when a uintptr\_t tf\_esp; uint16\_t tf\_ss; uint16\_t tf\_padding4; \_attribute\_\_((packed));

- Page Fault

- We run 1,000,000 instances of /bin/bash in our os2 server, running Linux enabled with copy-on-write fork(). How many copies of the code (the read-only part) of /bin/bash exist in the physical memory?

- One, shared via copy-on-write

- How can an OS run a program that requires more memory than a machine's physical memory?

- We can store currently unused memory pages in the disk (swap-out)

- Accessing to swapped-out pages will generate a page fault

- The OS can search for swapped-out pages, and fill a page in if exists (swap-in)

- Resumes user execution!

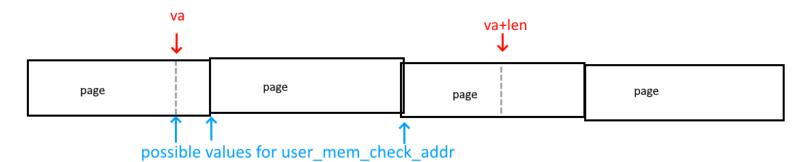

# Tips for Lab 3

Pic credit to Jonathan Keller

#### Tips for Lab 3 weird edge cases with user\_mem\_check

user\_mem\_check\_addr must be the FIRST invalid address in the range [va, va+len]

Because all addresses in a given page have the SAME permissions, an address can only go from valid to invalid at the start of a page.

This means that the FIRST invalid address must either be:

The first address in a given page (i.e. page-aligned)

•va itself (for when the first page is invalid) (not necessarily page-aligned)

Remember that user\_mem\_check\_addr must still be within the [va, va+len] range!

Pic credit to Adrian Baker