## **CS 271 Computer Architecture and Assembly Language**

## Self-Check for Lecture#18

## Solutions are posted

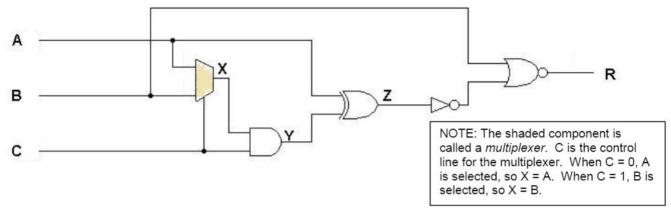

- 1. Show the truth table for the circuit shown above. Columns X, Y, and Z are for your convenience if you want to save intermediate results.

- 2. Find a Boolean equation to describe the circuit shown above.

$R = A\overline{BC} + A\overline{BC}$  Use Lines where R = 1

| 3. | (Optional Challenge) Reduce R to its simplest form. |

|----|-----------------------------------------------------|

|    | Show your simplification steps.                     |

| A | В | C | Х | Y | Z | R |

|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 | 0 | 0 |

| $R = A\overline{B}(\overline{C} + C)$ | Distributive Law |

|---------------------------------------|------------------|

| $R = A\overline{B}(1)$                | Inverse Law      |

| $\overline{D} = A\overline{D}$        | Identity I aw    |

4. It takes one clock cycle to perform an addition operation in the 4-bit ripple-carry adder (see Lecture slide page 7). How many clock cycles will it take for one addition instruction to be executed in a 64-bit ripple-carry adder?

\_\_\_\_1\_\_\_ clock cycles

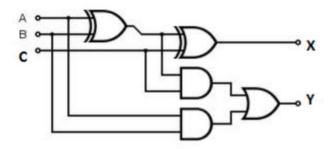

5. The circuit below should be familiar to you, even though it is in a slightly different configuration from the lecture. What does the circuit do? What are the inputs? What results are expected at X and at Y?

It's just a full adder. Inputs A and B are corresponding bits of two binary numbers that are to be added. Input C is "carry in". Output X is the sum bit, and output Y is the "carry out" bit.